PCI 的定义

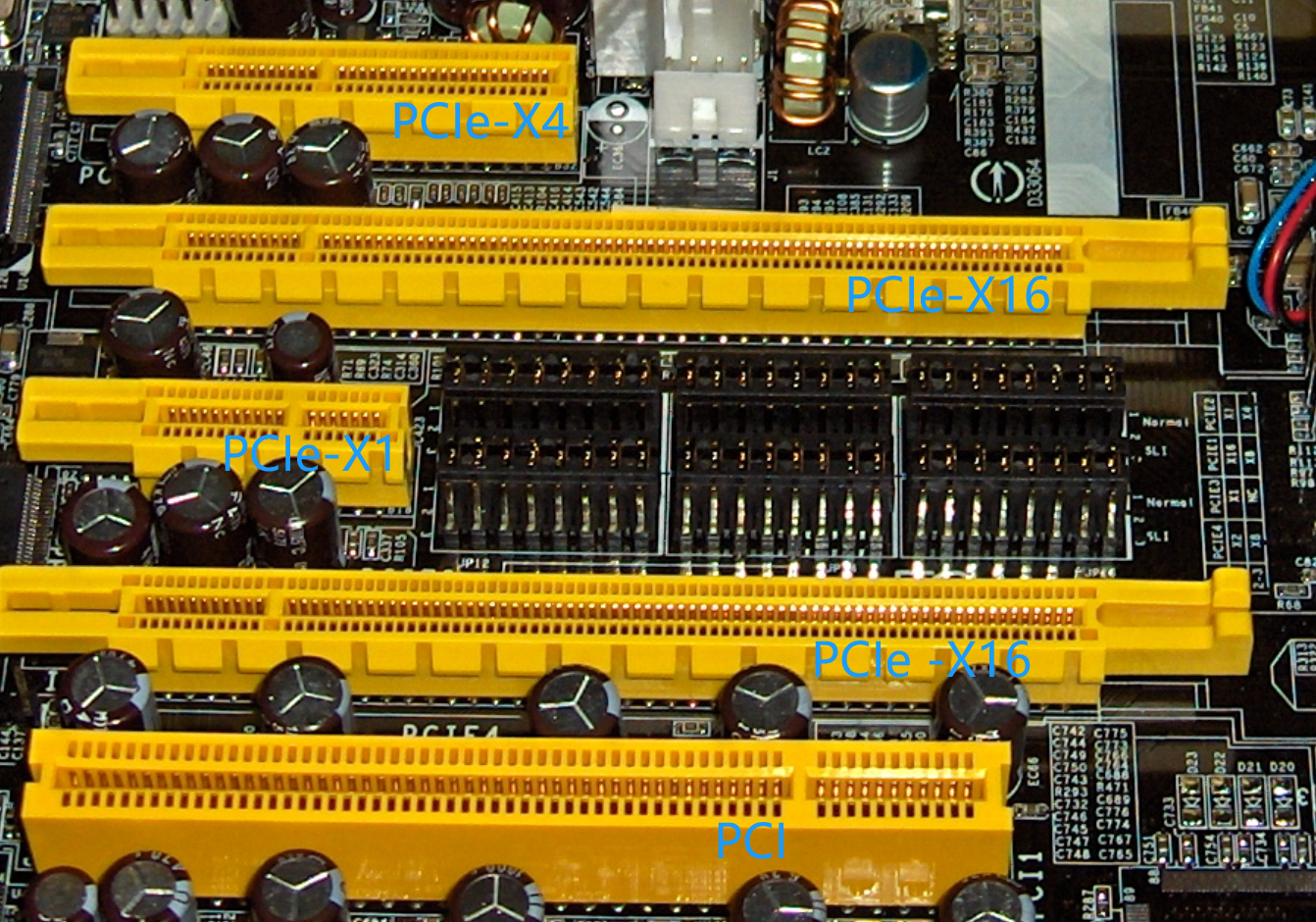

PCI(Peripheral Component Interconnect,外围组件互联) 是一种由 Intel 于 1992 年 提出的 并行总线标准,用于连接计算机主板与各类扩展设备(如显卡、网卡、声卡等)。早期的计算机用的是PCI技术,受于人们对性能要求越来越高,PCI技术存在明显的瓶颈,目前已由PCI进化到PCIe(Peripheral Component Interconnect Express)技术了。不同版本的PCIe接口,如PCIe x1、PCIe x4、PCIe x8、PCIe x16等,在物理长度和针脚数量上有所区别,但基本结构相似。

PCI插槽与PCIe插槽图物理区别如下图:

PCI 的用途

PCI 主要用于 扩展计算机功能,允许用户插入不同的硬件设备,例如:

- 显卡(独立显卡,如 NVIDIA RTX系列,AMD RT系列)。

- 网卡(有线/无线网络适配器)。

- 声卡(专业音频设备)。

- 固态盘(U.2固态硬盘)。

- 存储控制器(如 SCSI、RAID 卡)。

- 其他扩展卡(USB 扩展卡、FPGA加速卡等)。

PCI技术发展简史

- PCI 1.0(1992年)

- 总线频率:33 MHz

- 传输速率:133 MB/s(32位总线)

- 特点:首次标准化并行总线,取代早期的ISA总线。

- PCI 2.0(1993年)

- 新增66 MHz工作频率(理论速率266 MB/s)。

- 支持36位地址空间(最大4 GB内存寻址)。

- 新增功能:中断请求排队、快速传输模式。

- PCI 2.1(1995年)

- 引入64位总线支持,理论速率提升至533 MB/s(64位@66 MHz)。

- 改进信号完整性,提升稳定性。

- PCI 2.2(1998年)

- 支持3.3V低电压信号,优化功耗管理。

- 增强缓存一致性(Cache Coherence)和错误报告机制。

- PCI 3.0(2002年)

- 新增8b/10b和8b/8b编码,提高信号效率。

- 支持数据包优先级和延迟事务(Latency Tolerance)。

- 注:带宽未提升,最终被PCIe取代。

PCIe(串行总线)发展历程

- PCIe 1.0(2003年)

- 传输速率:2.5 GT/s(实际带宽 250 MB/s per lane,x16通道4 GB/s)。

- 编码方案:8b/10b(效率80%)。

- 支持x1、x4、x8、x12、x16通道配置。

- PCIe 2.0(2007年)

- 速率翻倍至5.0 GT/s(x16带宽8 GB/s)。

- 保留8b/10b编码,兼容PCIe 1.0设备。

- PCIe 3.0(2010年)

- 速率提升至8.0 GT/s(x16带宽15.75 GB/s)。

- 编码升级为128b/130b(效率98.5%)。

- 新增x32通道(主要用于服务器)。

- PCIe 4.0(2017年)

- 速率翻倍至16.0 GT/s(x16带宽31.51 GB/s)。

- 保持128b/130b编码,但信号完整性要求更高。

- PCIe 5.0(2019年)

- 速率再翻倍至32.0 GT/s(x16带宽63 GB/s)。

- 引入PAM4调制技术,支持AI/数据中心应用。

- PCIe 6.0(2022年发布)

- 速率达64.0 GT/s(x16带宽126 GB/s)。

- 采用PAM4编码+低延迟FEC纠错,面向HPC和AI。

PCI与PCIe关键技术性能对比

| 版本 | 类型 | 发布时间 | 速率/带宽 | 主要改进 |

|---|---|---|---|---|

| PCI 1.0 | 并行总线 | 1992 | 133 MB/s | 取代ISA,标准化扩展槽 |

| PCI 2.1 | 并行总线 | 1995 | 533 MB/s(64位) | 支持64位扩展 |

| PCIe 1.0 | 串行总线 | 2003 | 2.5 GT/s(4 GB/s) | 首代串行化,取代PCI |

| PCIe 3.0 | 串行总线 | 2010 | 8 GT/s(16 GB/s) | 高效128b/130b编码 |

| PCIe 5.0 | 串行总线 | 2019 | 32 GT/s(63 GB/s) | 支持PAM4,AI/数据中心首选 |

| PCIe 6.0 | 串行总线 | 2022 | 64 GT/s(126 GB/s) | PAM4+FEC,面向超算 |

声明:欢迎大家光临本站,学习IT运维技术,转载本站内容,请注明内容出处”来源刘国华教育“。如若本站内容侵犯了原著者的合法权益,请联系我们进行处理。